Herzlich Willkommen beim beam-Verlag in Marburg, dem Fachverlag für anspruchsvolle Elektronik-Literatur.

Wir freuen uns, Sie auf unserem ePaper-Kiosk begrüßen zu können.

10-2020

- Text

- Technik

- Verstaerker

- Antennen

- Komponenten

- Technik

- Radio

- Filter

- Emv

- Wireless

- Messtechnik

- Bauelemente

- Quarz

- Oszillator

- Software

- Quarze

- Oszillatoren

Fachzeitschrift für Hochfrequenz- und Mikrowellentechnik

Titelstory

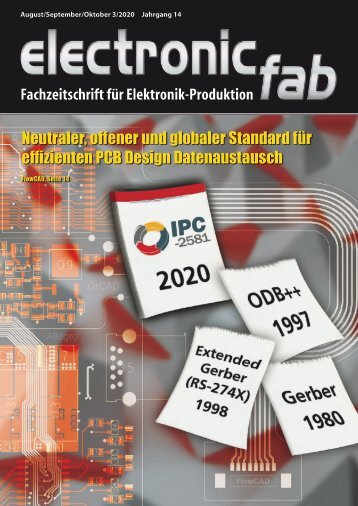

Titelstory Design-Flow-Integration von EM-Analyse in System und Circuit Design austausch wird aber nicht nur die Cadence-Software unterstützt, Formate wie Gerber, IPC-2581 und ODB++ lassen auch den Datenaustausch mit PCB Tools anderer Hersteller zu. Frühzeitig Fehler vermeiden ist immer wichtig: Zeit und Kosten, die erforderlich sind, um einen Fehler zu beheben, steigen exponentiell an, je später dieser im Entwicklungsprozess erkannt wird. Wird eine Fehlerursache erst in einer Messung an den Prototypen in der EMV-Kammer entdeckt, sind bereits Wochen vergangen und Kosten für die Messungen und die Prototypen entstanden. Wenn der Fehler bereits während der Entwicklung durch Simulation entdeckt und vermieden werden kann, sind die Auswirkungen auf die Zeit bis zum Markteintritt gering. Dies führt zu der Forderung, so früh wie möglich die Design-Regeln einzuhalten und die Robustheit von Teilen der Schaltung zu verifizieren. Mit der neuen Version V15 können große Strukturen von Leiterplatten aus den OrCAD oder Allegro PCB Design Tools oder über IPC-2581 und ODB++ aus anderer Layout Software eingelesen und verwendet werden. Die großen Strukturen ganzer Systemleiterplatten können jetzt schnell und ohne Zeitverlust einer EM-Analyse mit Unterstützung durch den PCB EM Setup Wizzard unterzogen werden. Integrierte 5G NR Testbench mit vorkonfigurierten Messungen und Analysen 46 hf-praxis 10/2020

Titelstory AWR Design Environment V15 Highlights Environment/ Automation Circuit Simulation EM Simulation System Simulation Physical Design/ Layout • Load-pull contours on rectangular plots • Template-based measurements • Add / edit optimization goals directly on graphs • Fast, rigorous stability analysis • Low-frequency load-pull for two-tone excitations • Integrated TX-Line calculator / synthesis • Faster, more robust adaptive meshing • Fast, accurate DC solver • Peak antenna measurements • Preconfigured 5G NR testbenches libraries • Phased array MIMO support bus • PA linearization with digital predistortion (DPD) • Real-time DRC compliant iNets routing guides • Mixed physical units / grid support • Two-click data entry mode • Edit axes directly on plots • Color-coded markers • Equation grouping • Network synthesis with PDK / vendor components • Resize layout objects with property page editing • Gerber file import for EM analysis Zur Optimierung von HF-Designs stehen im AWR Design Environment elektromagnetische (2,5D und volle 3D), lineare und nichtlineare Solver (sowohl im Frequenz- als auch im Zeitbereich) zur Verfügung. Die unterschiedlichen Lösungen ermöglichen es, bereits im Schaltplan mit den verfügbaren Informationen, z.B. die Impedanz für einen Leiterplatten-Lagenaufbau, der aus den PCB Tools bereits bekannt ist, zu simulieren. Je weiter die Entwicklung voranschreitet, können auch Teile des Layouts sofort simuliert und optimiert werden. Im neuen Release sind die Analysezeiten weiter verbessert worden, sodass in gleicher Zeit mehrere Alternativen getestet und verglichen werden können. AWR verfügt mit Axiem über einen Planar-Solver nach der Methode der Momente (MoM) sowie mit Analyst über einen 3D-FEM-EM-Simulator. Aber auch Schnittstellen zu anderen Simulatoren von Cadence auf Systemebene, wie Spectre, Celsius, Clarity oder anderen, sind je nach dem Bedarf der Ingenieure verfügbar. Standards virtuell testen zu können, ist ebenso wichtig: Neue Frequenzbereiche und neue Anwendungen haben auch neue Standards hervorgebracht. Fertige Produkte müssen diese Standards erfüllen und deren Einhaltung wird später durch Messungen bestätigt. Die AWR-Entwicklungswerkzeuge enthalten bereits viele virtuelle Testaufbauten, um die Einhaltung der Standards schon mit den Design-Daten zu verifizieren, bevor ein Prototyp gebaut und eine Zeit im Messlabor beantragt wurde. In Bibliotheken gibt es leicht zu konfigurierende Signalquellen und Empfänger, die zur Evaluierung der eigenen Schaltung zu Testaufbauten zusammengeschaltet werden können. In V15 ist eine Bibliothek für 5G NR hinzugekommen und die AWR Knowledge Base wurde um entsprechende 5G-Beispielprojekte erweitert, die nach den Vorgaben des 3. Generation Partnership Project (3GPP) konfiguriert wurden. So können HF- Schaltungsteile und HF-Komponenten in vorkonfigurierten RX- und TX-Blöcken verwendet werden, um die Uplink- und Downlink-Funktion des gesamten Systems virtuell gegen den Standard zu testen. Die Signale lassen sich für Sub- 6-GHz- (FR1) und Millimeterwellen-Bänder (FR2) flexibel konfigurieren. Die Parameter für eine variable Signalleistung, die Trägerfrequenz, die Modulation, das Codier-Verfahren (MCS) wie auch die Bandbreite lassen sich einstellen. Zu den verfügbaren Messungen gehören auch Bit Error Rate (BER), Block Error Rate (BLER) und Durchsatz. Die neue 5G NR TX Testbench unterstützt Sendersimulationen und Bauteilvalidierungen mit vielfältigen vorkonfigurierten Messungen zur Analyse der Leistungsmatrix wie Complementary Cumulative Distribution Function (CCDF), AM zu AM/PM, Spektrum, Error Vector Magnitude (EVM), Adjacent Channel Power Ratio (ACPR) und IQ Constellation. Für das Sub-6GHz-Band (FR1) und das Millimeterwellenband (FR2) gibt es fertige Downlink- Testmodelle für 5G-NR-Signale zum Test von Basestation Output Power, unerwünschten und nicht erlaubten Emissionen, Intermodulationen, EVM für unterschiedliche Modulationen wie Quadrature Phase Shift Keying (QPSK) und 16, 64 oder 256 Quadrature Amplitude Modulation (QAM) sowie Frequency Error. Neue Analysen und neue Funktionen in der Schaltungssimulation ermöglichen eine schnelle und strenge nichtlineare Stabilitätsanalyse für mehrstufige und symmetrische Verstärker sowie Videoband Load Pull zur Optimierung von Niederfrequenz- Impedanzabschlüssen für reduzierte Intermodulationsverzerrungen. Die Load-Pull-Technik wird traditionell verwendet, um die Impedanz eines nichtlinearen HF-Geräts bei maximaler HF- Leistung zu messen. Die Lastimpedanz (Load) wird so manipuliert, dass diese einen vom definierten Ohm-Wert abweichenden Wert annimmt. Das Verhalten der Schaltung auf die verschiedenen Impedanzen kann untersucht werden. Die Synthese und die Simulation von Transmission Lines sind bereits im Schaltplan möglich. Große Strukturen, wie sie bei komplexen Leiterplatten vorkommen, können in einer EM-Analyse mit einem Feldlöser berechnet werden. Dabei beschleunigt ein optimiertes Meshing mit Smart-Geometry- Methoden die Analysezeiten und der Entwickler kommt schnell zu robusten und belastbaren Ergebnissen. Weiterhin bietet das AWR Design Environment V15 einen neuen Digital Pre-Distortion (DPD) Block mit Algorithmen zur Optimierung von linearen und nichtlinearen Verstärkern. Auch hierzu gibt es in der Bibliothek entsprechende Beispielschaltungen, die ein schnelles Verständnis der Analysen ermöglichen. Bei automatisierten Schaltungsoptimierungen können die Entwickler Ziele für die Optimierung jetzt direkt grafisch in den Anzeigen (Plots) definieren. Designregeln lassen sich vorgeben und werden beim regelkonformen Routen der HF-Leitungen als intelligent Nets (iNets) in Echtzeit umgesetzt. ◄ hf-praxis 10/2020 47

- Seite 1 und 2: Oktober 10/2020 Jahrgang 25 HF- und

- Seite 3 und 4: Editorial Einstein würde staunen:

- Seite 5 und 6: JYEBAO International News Dual PIN

- Seite 7 und 8: SIX DAYS THREE CONFERENCES THREE FO

- Seite 9 und 10: ® B E YO N D R E A LT I M E Techni

- Seite 11 und 12: FOR ALL INNOVATIVE TEST LABS REMOTE

- Seite 13 und 14: Die Cloud ist grenzenlos Der einfac

- Seite 15 und 16: Quarze und Oszillatoren Leck, das d

- Seite 18: Quarze und Oszillatoren TCXOs für

- Seite 22 und 23: Quarze und Oszillatoren Quarz- und

- Seite 24 und 25: Quarze und Oszillatoren Oszillators

- Seite 26 und 27: Quarze und Oszillatoren Crystal Rea

- Seite 28 und 29: Quarze und Oszillatoren Vin + - + -

- Seite 30 und 31: Rx1 Rx2 +5V EXTAL Cx Bild 6: Modell

- Seite 32 und 33: Quarze und Oszillatoren Oszillatore

- Seite 34 und 35: Quarze und Oszillatoren Kosteneinsp

- Seite 36 und 37: Quarze und Oszillatoren VCOCXOs arb

- Seite 38 und 39: APPLICATION SPOTLIGHT RF PCB Design

- Seite 40 und 41: APPLICATION SPOTLIGHT RFIC/SiP Desi

- Seite 42 und 43: RESOURCE SPOTLIGHT Best of ADF Now

- Seite 44 und 45: RESOURCE SPOTLIGHT On-Demand Webina

- Seite 48 und 49: Bauelemente Neue Entstörkondensato

- Seite 50 und 51: Bauelemente Verlustarmer Koaxialada

- Seite 52 und 53: Kabel und Stecker Testkabel-Set fü

- Seite 54 und 55: Kabel und Stecker Testkabel für Fr

- Seite 56 und 57: Funkchips und -module HF-Transceive

- Seite 58 und 59: Messtechnik Echtzeit-Spektrumanalys

- Seite 60 und 61: Messtechnik Bild 5: RSA5065N: GPSA-

- Seite 62 und 63: Messtechnik Scope bietet vier Kanä

- Seite 64 und 65: Messtechnik Automatische EMV-Messun

- Seite 66 und 67: Messtechnik Testumfang des R&S TS89

- Seite 68 und 69: 5G und IoT Lösungen bei schwierige

- Seite 70 und 71: 5G und IoT Bild 3: SiTime-MEMS-Oszi

- Seite 72 und 73: RF & Wireless Richardson Electronic

- Seite 74 und 75: RF & Wireless Modular 2-Port VNA Fa

- Seite 76 und 77: www.minicircuits.com (718) 934-4500

- Seite 78: RF & Wireless/Impressum Comprehensi

Unangemessen

Laden...

Magazin per E-Mail verschicken

Laden...

Einbetten

Laden...

hf-praxis

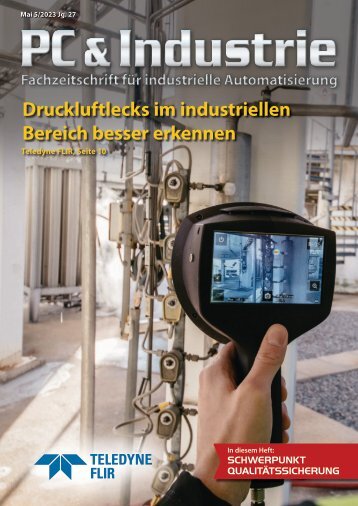

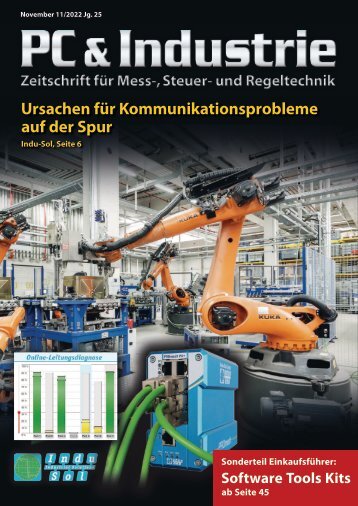

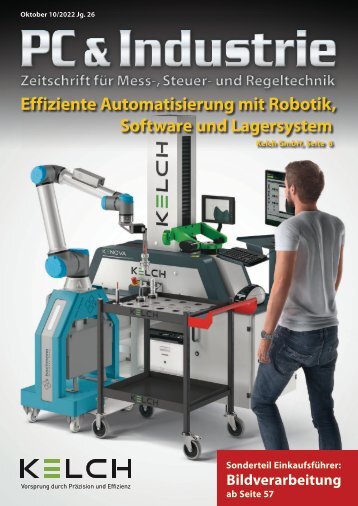

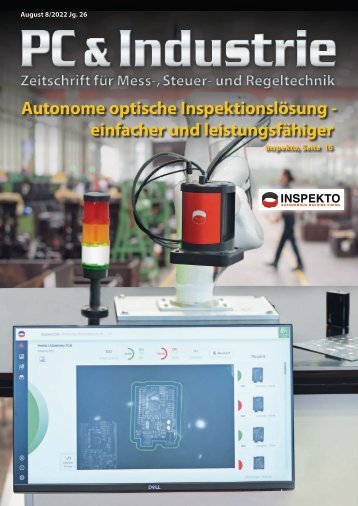

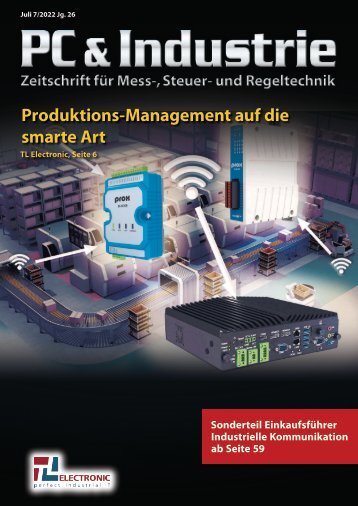

PC & Industrie

meditronic-journal

electronic fab

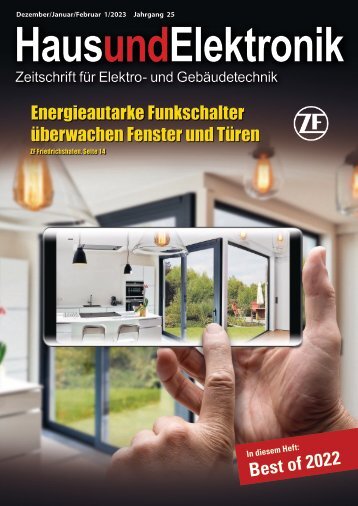

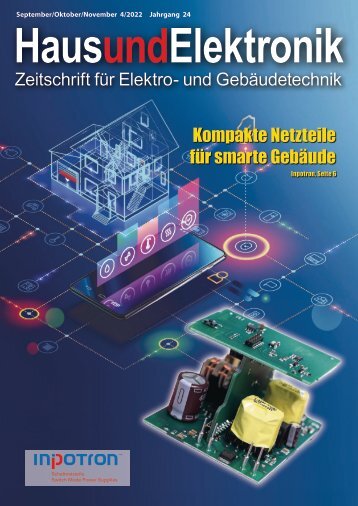

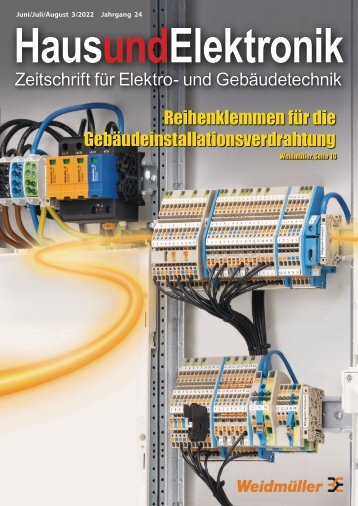

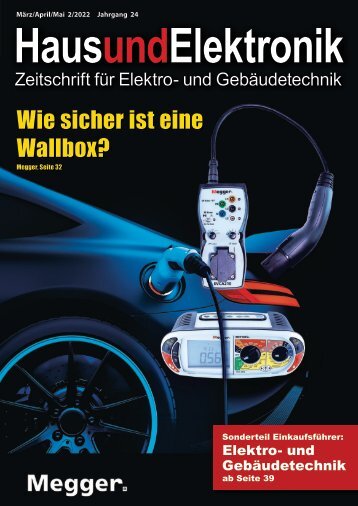

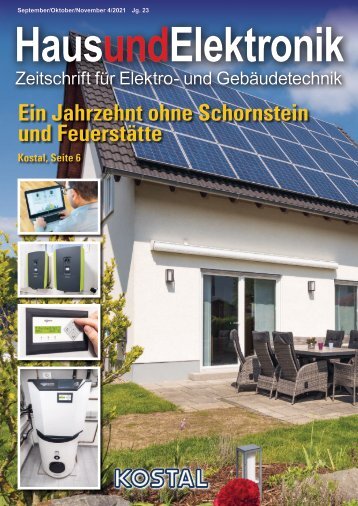

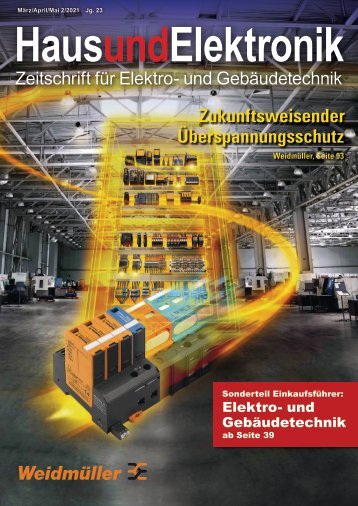

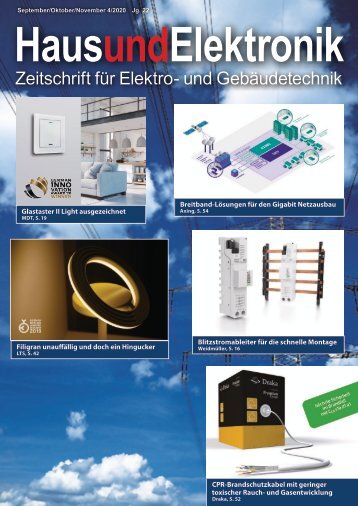

Haus und Elektronik

Mediadaten

© beam-Verlag Dipl.-Ing. Reinhard Birchel