Herzlich Willkommen beim beam-Verlag in Marburg, dem Fachverlag für anspruchsvolle Elektronik-Literatur.

Wir freuen uns, Sie auf unserem ePaper-Kiosk begrüßen zu können.

7-2015

- Text

- Technik

- Radio

- Oszillatoren

- Quarze

- Emv

- Messtechnik

- Bauelemente

- Antenna

- Amplifier

- Wireless

- Components

- Frequenz

- Mikrowellentechnik

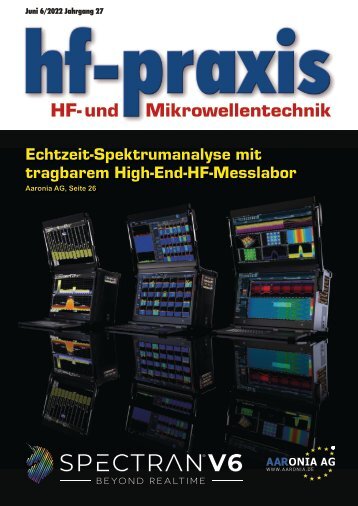

Fachzeitschrift für Hochfrequenz- und Mikrowellentechnik

Bauelemente

Bauelemente Leistungsfähiger Mixed-Signal-Frontend- Baustein Das neue IC AD9993 von Analog Devices integriert vier 14-Bit- ADCs und zwei 14-Bit- DACs sowie die Takterzeugung. Bild 1: Verlustarme, galvanisch getrennte Eingangskopplung mit Transformator Quelle: Analog Devices: Integrated Mixed-Signal Front End (MxFE) AD9993 Der AD9993 ist ein junges Mitglied der Highspeed-CMOS- DAC-Core-Familie von Analog Devices. Diese DACs wurden besonders für den Einsatz in breitbandigen Sendern für Kommunikationssysteme entwickelt. Die ADCs in diesem Mixed-Signal-Frontend-Baustein basieren auf mehrstufigen CMOS-ADC-Kernkonzepten und wurden für die Verwendung in Kommunikationsempfängern geschaffen. Allgemein lässt sich der AD9993 besonders gut in Point-to-Point- Funkanwendungen im Mikrowellenbereich und in drahtlosen Repeatern einsetzen. ADC-Architektur Die kompletten Analog/Digital-Wandler im AD9993 besitzen eine duale Frontend- Sample&Hold-Schaltung und bilden im Prinzip eine kaskadierte Reihe von Switched- Capacitor-ADCs. Die quantisierten Ausgangssignale von jeder Stufe werden zu einem 14-Bit-Endresultat verknüpft. Die Eingangsstufe jedes ADC- Kerns enthält eine differentielle Sampling-Schaltung, welche AC- oder DC-gekoppelt und auch im Single-ended- Betrieb genutzt werden kann. Der differentielle Switched- Capacitor-Teil im Eingang der ADCs entfaltet nur im Differenzbetrieb seine optimale Performance. Für Basisband- Applikationen, wo das SNR ein Schlüsselparameter ist, sollten daher entsprechende Transformatoren/Baluns vorgeschaltet werden. Für ein Vorspannen des analogen Eingangs kann man die Spannung V CM nutzen, die man einer Mittelanzapfung des Trafos zuführt. Bild 1 bringt die Konfiguration mit einem Differential- Transformator. Die Kopplung mit einem zweifachen Balun zeigt Bild 2. Auch hier ist der ADC-Eingang AC-gekoppelt, und die Spannung V CM wird durch die 33-Ohm-Widerstände gesplittet. Diese erzeugen entsprechende Verluste. Zu den DACs Die DACs besitzen zwei differentielle Stromausgänge. Das Datenblatt hält Formeln bereit, mit denen die entsprechenden DAC-Ausgangsströme bestimmt werden können. Jeder DAC besitzt seinen eigenen I REF -Setzwiderstand. Hier lassen sich auch externe Wichtige Kennzeichen des AD9993 • Quad 14-Bit 250 MSPS ADC mit SFDR = 83 dBc bei 87 MHz (Input) • Dual 14-Bit 500 MSPS DAC mit SFDR = 75 dBc bei 20 MHz (Output) • On-Chip PLL Clock Synthesizer • Low Power (1.536 mW) • 1 GHz Master Clock • LVDS Interfaces für DACs und ADCs • 12x12 mm großes BGA-Gehäuse 42 hf-praxis 7/2015

Bauelemente Bild 2: Breitbandige Kopplung mit doppeltem Balun, Eingangsimpedanz 50 Ohm Widerstände nutzen. Der Nennwert ist 1,6 kOhm, die Nennreferenz 1 V. Diese kann von der On- Chip-Bandgap-Quelle stammen oder von einer äußeren Quelle. Optimale DAC-AC-Performance wird erreicht, wenn die Gleichtaktspannung am Ausgang zwischen 0 und 0,5 V liegt und das Signal in den Compliance- Bereich fällt. Der AD9993 enthält auch einen abstimmbaren DDS (Direct Digital Synthesizer) zur DAC-Ausgangston-Generierung. Er lässt sich als digitale Signalquelle der beiden DACs aufschalten. Die Daten an ADCs und DACs Die Datenpfade der ADCs und DACs umfassen auch FIFO- Buffer, um die Phasendifferenzen zwischen den beiden Taktsignalen aus LVDS Lane und Datenkonverter (Sampling- Takt) zu neutralisieren. Das DAC-Daten-Interface bietet sechs DDR LVDS Data Lanes für jeden DAC und eine gemeinsame Taktquelle. Das ADC-Daten-Interface enthält vier DDR LVDS Data Lanes für jeden ADC, eine gemeinsam genutzte Taktquelle sowie einen gemeinsamen Strobe-Ausgang. DDR steht für Double Data Rate und kennzeichnet einen speziellen Speichertyp. LVDS bedeutet Low-Voltage Differential-Signaling und ist ein Schnittstellenstandard für die Hochgeschwindigkeits-Datenübertragung. Die Signale werden mit einer Konstantstromquelle erzeugt. Zur Takterzeugung Bild 3 gibt einen Überblick über das gesamte Takterzeugungssystem an Bord des AD9993. Die Taktsignale für die LVDS Lanes, die DACs und die ADCs stammen aus einer einzigen Master-Quelle. Dieses Signal wird entweder direct an die CLKP/CLKN-Pins gelegt oder von einem On-Chip PLL Multiplier als Referenz genutzt. ADC Output und DAC Input LVDS Lanes laufen mit der Master-Taktfrequenz, geteilt durch 2 und sind DDR-Signale (Double Data Rate). Die Sampling Rate der ADCs beträgt ein Viertel der Master Clock Rate, die Sampling Rate der DACs die Hälfte davon. Mit 1 GHz Master Clock erhält man also die anderen On-Chip-Größen zu: • DCO (ADC DDR LVDS Output Lane Clock) 500 MHz • DCI (DAC DDR LVDS Input Lane Clock) 500 MHz • DAC Sampling Rate 500 MSPS • ADC Sampling Rate 250 MSPS Der PLL-Taktgenerator Die benötigten Taktsignale können von einer externen Quelle geliefert werden oder von einem integrierten On-Chip-PLL-Multiplizierer, welcher einen externen Referenzoszillator nutzt. hf-praxis 7/2015 43

- Seite 1 und 2: Juli 7/2015 Jahrgang 20 HF- und Mik

- Seite 3 und 4: Editorial Autor: Dipl. Ing. Frank S

- Seite 5 und 6: 7/2015 EMV: RF & Wireless Internati

- Seite 8 und 9: Messtechnik Bild 1 zeigt den gesamt

- Seite 10 und 11: Messtechnik Graphik 2: Messaufbau f

- Seite 12 und 13: Produkt-Portrait 15-GHz-HF-Leistung

- Seite 14 und 15: Messtechnik Oszilloskope zum Testen

- Seite 16 und 17: Messtechnik Elektromagnetische Gebi

- Seite 18 und 19: Messtechnik Vektorieller Netzwerk-A

- Seite 20 und 21: HF-Technik Ultra-breitbandiger und

- Seite 22 und 23: HF-Technik Während der Betrieb ein

- Seite 24 und 25: Design Leiterplattenstrukturierung

- Seite 26 und 27: Praxiseinstieg in die Spektrumanaly

- Seite 28 und 29: Quarze & Oszillatoren Quarzplättch

- Seite 30 und 31: Quarze & Oszillatoren LVDS-Oszillat

- Seite 32 und 33: EMV Messungen von hochfrequenten Na

- Seite 34 und 35: EMV EMV-Abschirmung mit leitfähige

- Seite 36 und 37: Applikationen 6-GHz-Differenzverst

- Seite 38 und 39: Applikationen Bild 11: Externe und

- Seite 40 und 41: Produkt-Portrait Verlustarmer 28-V-

- Seite 44 und 45: Bauelemente Bild 3: Die Taktsteueru

- Seite 46 und 47: Bauelemente 75-Ohm-Diplexer für DC

- Seite 48 und 49: Test & Measurement LCR Meter Provid

- Seite 50 und 51: RF & Wireless Microwave Components

- Seite 52 und 53: RF & Wireless Components MACOM Intr

- Seite 54 und 55: RF & Wireless Components RFMW Intro

- Seite 56 und 57: RF & Wireless Figure 6. The simulat

- Seite 58 und 59: RF & Wireless (Figure 9), so that t

- Seite 60 und 61: pwrSplitsprd448revN.indd 1

- Seite 62 und 63: Aktuelles/Fachliteratur/Impressum N

Unangemessen

Laden...

Magazin per E-Mail verschicken

Laden...

Einbetten

Laden...

hf-praxis

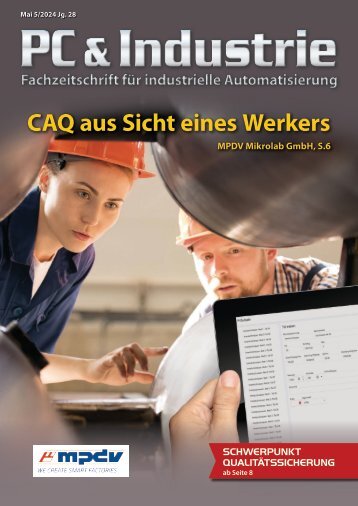

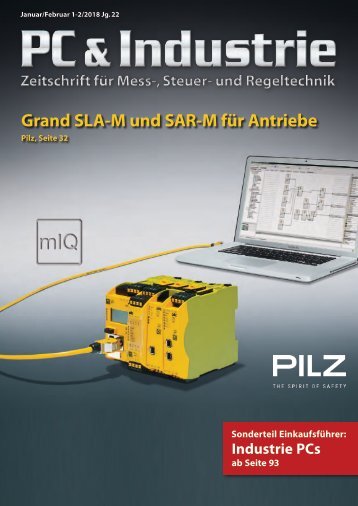

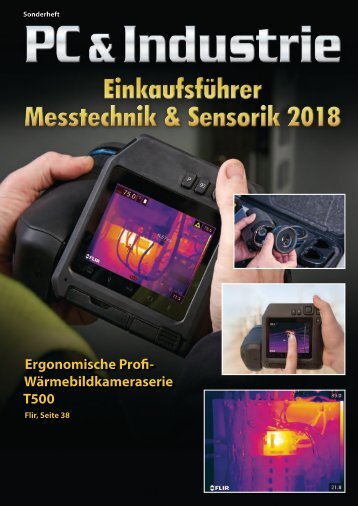

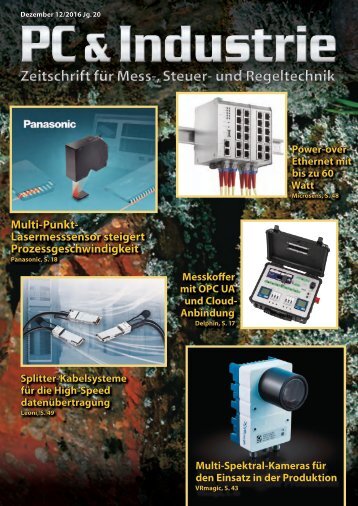

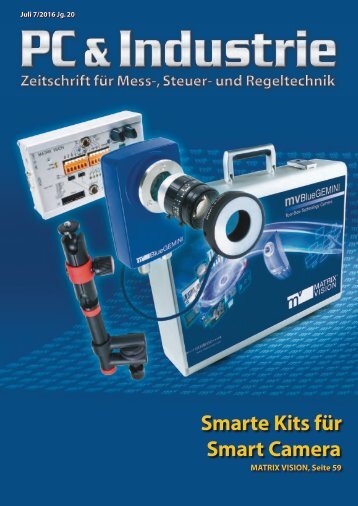

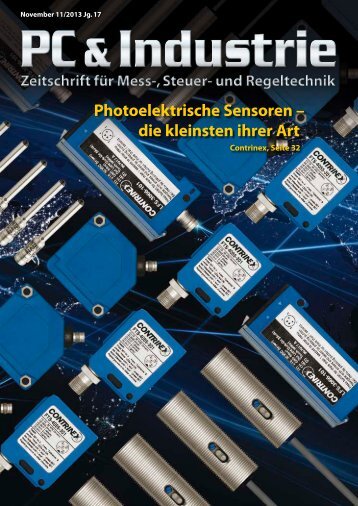

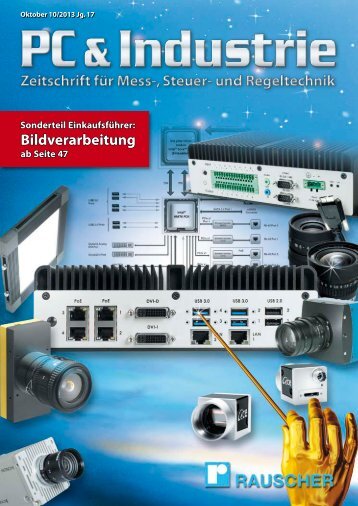

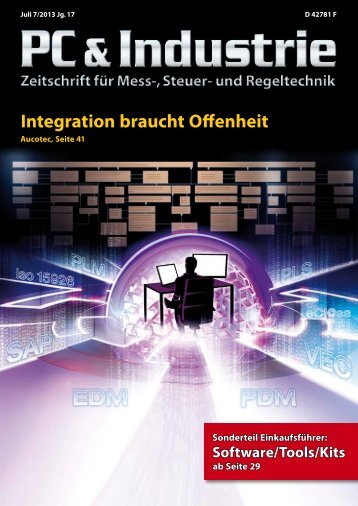

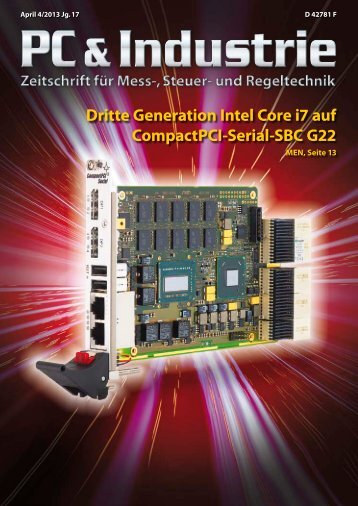

PC & Industrie

meditronic-journal

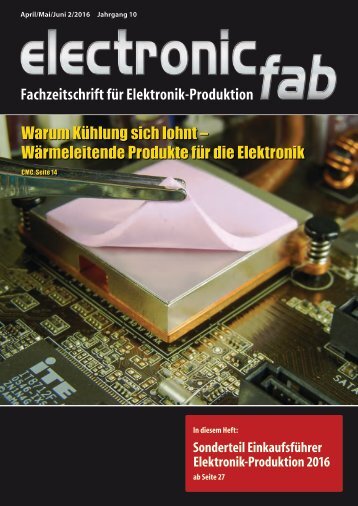

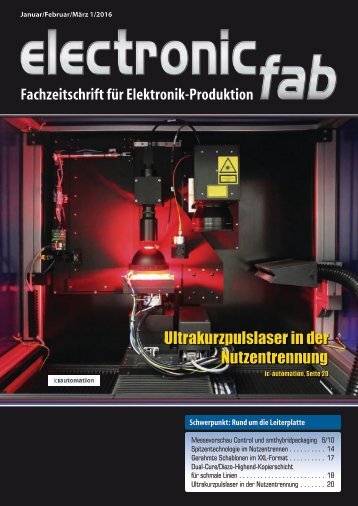

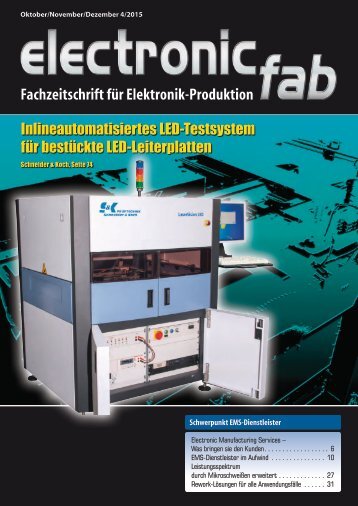

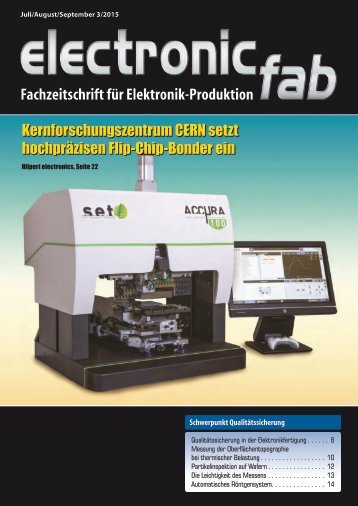

electronic fab

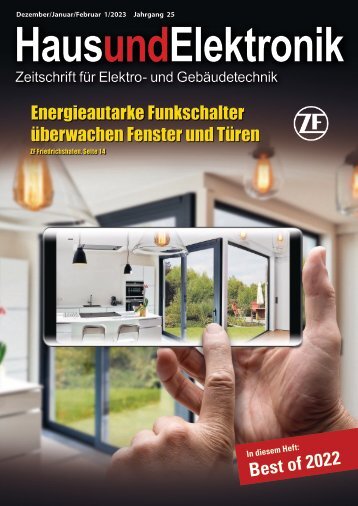

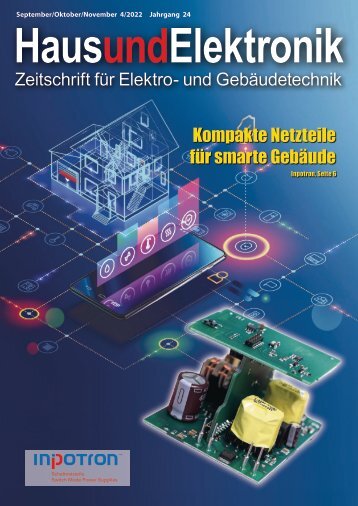

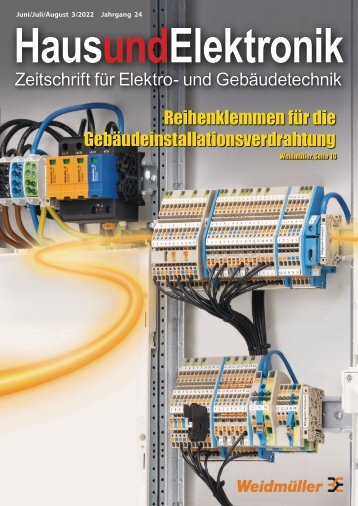

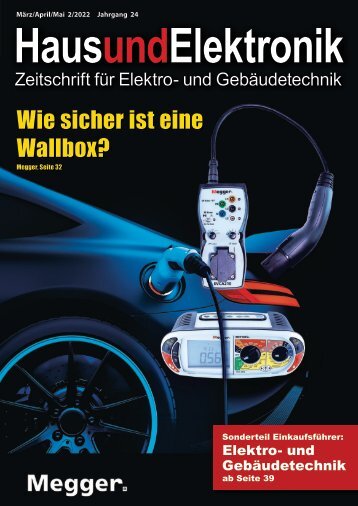

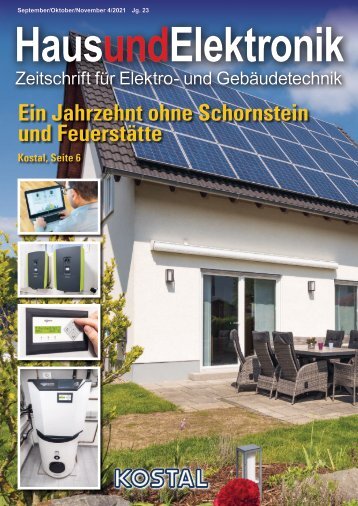

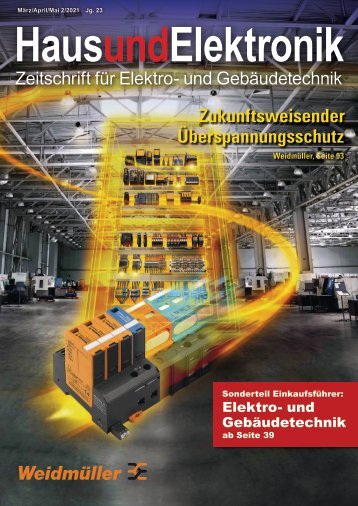

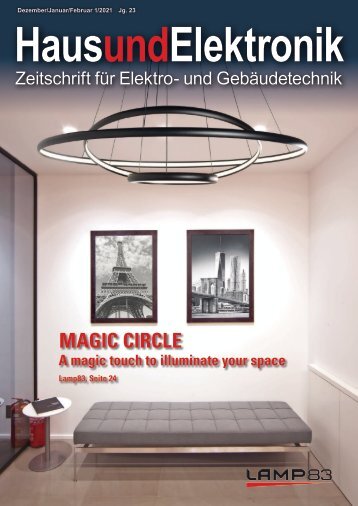

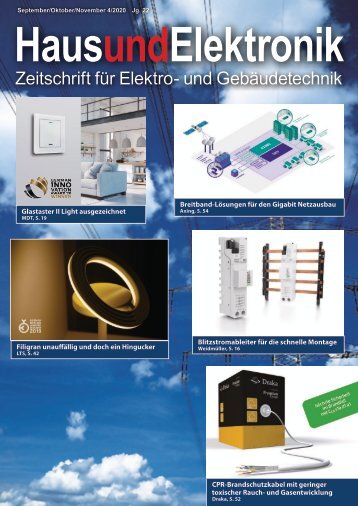

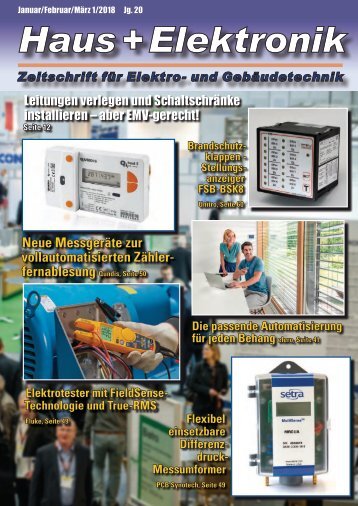

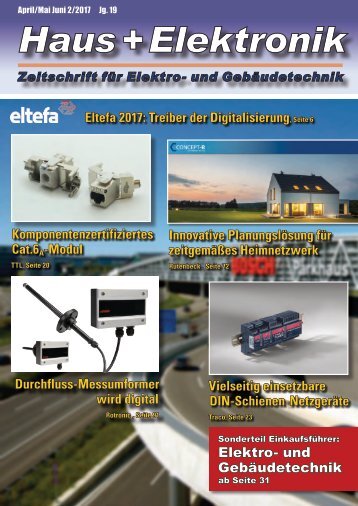

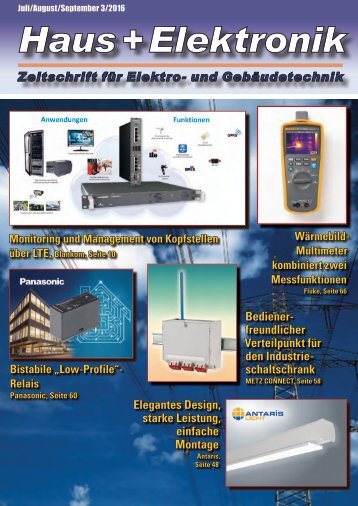

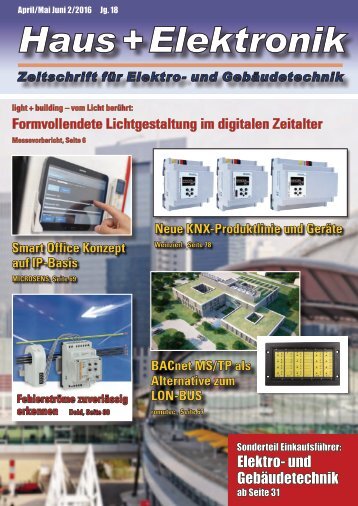

Haus und Elektronik

Mediadaten

© beam-Verlag Dipl.-Ing. Reinhard Birchel