Herzlich Willkommen beim beam-Verlag in Marburg, dem Fachverlag für anspruchsvolle Elektronik-Literatur.

Wir freuen uns, Sie auf unserem ePaper-Kiosk begrüßen zu können.

3-2020

- Text

- Technik

- Verstaerker

- Antennen

- Komponenten

- Technik

- Radio

- Filter

- Oszillatoren

- Quarze

- Emv

- Bauelemente

- Messtechnik

- Frequency

- Wireless

- Filters

- Filter

Fachzeitschrift für Hochfrequenz- und Mikrowellentechnik

EMV Bild 5: (a)

EMV Bild 5: (a) Idealfall, (b) zu lange HF-Übertragungsleitung, (c) nicht übereinstimmende Teile einer HF-Leitung Dielectric Layer Digital Trace in Ground Plane Bild 6: Digitale Leitungen direkt unter dem HF-Pfad anzuordnen, da dann die Kopplung minimal ist. Der erste Schritt zum Erstellen eines HF-Leiterplatten-Layouts besteht darin, die Eigenschaften der Leiterplatte zu verstehen, d.h., die dielektrischen (Dielektrizitätskonstante und Verlustfaktor) und die mechanischen Eigenschaften (Maße). Gute Entwürfe umfassen ein Dokument, das die Stapelbarkeit von Leiterplatten und deren Eigenschaften beschreibt, wie Stapelhöhe, Dielektrizitätskonstante und Verlustfaktor des Dielektrikums der Leiterplatte. Wenn das Design die Übersetzung eines zweilagigen Referenz-Designs auf eine vierlagige Leiterplatte erfordert, dann kann sich die Höhe zwischen der oberen Schicht und der Grundebene ändern. Das ändert die Impedanz des HF-Pfads. Die Änderung der Impedanz im HF-Pfad muss man durch Anpassen der Breite der Leiterbahnen berücksichtigt, wie im Anwendungshinweis AN068 [2] erläutert. Die folgende Check-Liste enthält wichtige Überlegungen zum HF- PCB-Design, die befolgt werden Ground Plane Top/Signal Layer müssen. Es wird dringend empfohlen, dass die Designer ihre Entwürfe mit den vorgeschlagenen Punkten überprüfen. Das Beachten dieser Punkte, die sich z.T. auf das TI-Referenz-Design beziehen, sollte dazu beitragen, eine optimale Leistung zu erzielen. • Stellen Sie sicher, dass Sie die für das Teil geltende Empfehlung zum Datenblatt-Layout befolgen. • 0603 (mils) messende diskrete Teile werden aufgrund ihrer Größe und ihrer parasitären Eigenschaften nicht empfohlen. • Stellen Sie sicher, dass die Überbrückungskondensatoren so nah wie möglich an den Stromversorgungsanschlüssen liegen. • Stellen Sie sicher, dass jeder Entkopplungskondensator nur die spezifischen empfohlenen Pins auf dem Referenz-Design entkoppelt und dass der Kondensator den richtigen Wert und Typ hat. • Stellen Sie sicher, dass die Entkopplung über die Verbindung Pin-Kondensator-Via erfolgt. • Vergewissern Sie sich, dass der Stapel mit dem Referenz- Design übereinstimmt. Wenn das Design eine vierlagige Leiterplatte ist, so vergewissern Sie sich, dass sich die Massefläche auf der zweiten Ebene direkt unter der Oberseite/ Komponentenseite befindet. • Das Ändern des Schichtabstands/-aufbaus wirkt sich auf die Anpassung im HF- Signalpfad aus und sollten sorgfältig berücksichtigt werden, wie in AN068 [2] erläutert. • Vergewissern Sie sich, dass die Massefläche mit dem Referenz-Design übereinstimmt. Es sollte eine feste Masseebene unter dem Gerät und dem HF- Pfad geben, jedoch keine leitende Ebene unter einer eventuellen Antenne, es sei denn, Sie verwenden eine Antenne, die die Massefläche als Gegengewicht nutzt (z.B. eine Peitschenantenne). 30 hf-praxis 3/2020

EMV Bild 7: Schlechte Bypass- Kondensator-Platzierung • Vergewissern Sie sich, dass der HF-Signalpfad so gut wie möglich mit dem Referenz-Design übereinstimmt. Komponenten sollten sehr ähnlich angeordnet Bild 8: Richtiges Bypassing-Layout und gleich ausgerichtet sein wie im Referenz-Design. • Ein Quarzoszillator sollte so nah wie möglich an den Anschlüssen entkoppelt und mit kurzen Signalleitungen weiterverbunden sein. Lange Leitungen zum Oszillator sollten nach Möglichkeit vermieden werden. • Vergewissern Sie sich, dass viele Durchkontaktierungen um den HF-Signalpfad existieren. Vias auf dem Rest der Platine sollten nicht mehr als λ/10 voneinander entfernt sein. • Verfügt das Design über einen Differenzialausgang, stellen Sie sicher, dass die Leitungen im Differenzialbereich symmetrisch ausgelegt werden. • Wenn für das Design eine Batterie (z.B. eine Knopfzelle) verwendet wird, fungiert die Batterie als Erdungsfläche und sollte daher nicht unter der Antenne platziert werden. • Vergewissern Sie sich, dass die Anordnung der Power-Pads unter dem Aufbau korrekt ist. Die Löt-Pads und die Maske sollten übereinstimmen und die Öffnungsgröße sollte die richtige Menge Paste gewährleisten. • Vias sollten die richtige Nummer haben und maskiert sein. • Die Karte sollte impedanzkontrollierte Leiterbahnen spezifizieren. Das heißt, der Schichtabstand bei FR4-Permittivität sollte kontrolliert und bekannt sein. Bild 9: Gewünschte Lagenfolge mit Impedanzdarstellung bei 2,4 GHz Bild 10: Unerwünschte Lagenfolge mit Impedanzdarstellung bei 2,4 GHz hf-praxis 3/2020 31

- Seite 1 und 2: März 3/2020 Jahrgang 25 HF- und Mi

- Seite 3 und 4: Editorial EMV 2020: Ein vielfältig

- Seite 5 und 6: Rubriken: 3 Editorial 4 Inhalt 6 Ak

- Seite 8 und 9: HF- und Mikrowellentechnik Schwerpu

- Seite 10 und 11: EMV Aktuelles Von der Idee bis zum

- Seite 12 und 13: EMV Messtechnik TDEMI ULTRA und EMI

- Seite 14 und 15: EMV Messtechnik Für den Einsatz zu

- Seite 16 und 17: EMV Messtechnik LO Frequenz M LO x

- Seite 18 und 19: EMV Messtechnik Superheterodyn Empf

- Seite 20 und 21: EMV Messtechnik Bild 5: Beispiel ei

- Seite 22 und 23: EMV Messtechnik Messtechnik und Pro

- Seite 24 und 25: EMV Messtechnik Relaisschaltfeld f

- Seite 26 und 27: EMV Messtechnik Funkstör-Messempf

- Seite 28 und 29: EMV RF PCB Design Basics EMV-gerech

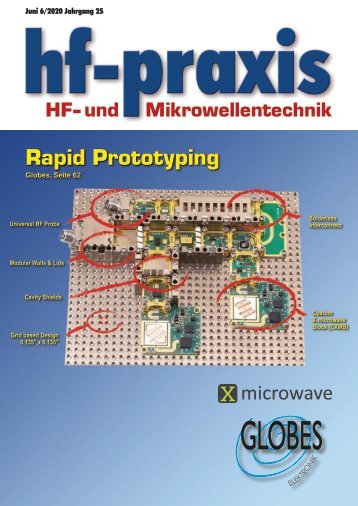

- Seite 32 und 33: EMV Das Aufmacherbild betrifft das

- Seite 34 und 35: EMV Einflüsse auf die Abschirmwirk

- Seite 36 und 37: EMV Bild 3: Abschirmwirkung eines d

- Seite 38 und 39: EMV Produkte Vielfältige Produkte

- Seite 40 und 41: EMV Die Problematik der Ferrit-Impe

- Seite 42 und 43: EMV danz anhand zweier verschiedene

- Seite 44 und 45: Messtechnik Modulares Messinstrumen

- Seite 46 und 47: THz-Technik Vergangenheit, Gegenwar

- Seite 48 und 49: THz-Technik Bild 3: Allgemeines Blo

- Seite 50 und 51: THz-Technik Bild 5: Allgemeine Send

- Seite 52: Wireless Robuste drahtlose Kommunik

- Seite 56 und 57: Bauelemente MMIC-Verstärker bietet

- Seite 58: Agreement for 5G NR Device Testing

- Seite 61 und 62: RF & Wireless acoustic resonators (

- Seite 63 und 64: RF & Wireless Figure 5: Properties

- Seite 65 und 66: RF & Wireless Figure 7: Microstrip

- Seite 67 und 68: Technology for Every Application! F

- Seite 69 und 70: RF & Wireless Figure 2: Frequency r

- Seite 71 und 72: RF & Wireless GaN Halfbridge Driver

- Seite 73 und 74: RF & Wireless Figure 2: Measured an

- Seite 75 und 76: RF & Wireless Differential Input Ga

- Seite 77 und 78: RF & Wireless Figure 3: RF/IF board

- Seite 80:

HANDHELD SPECTRUM ANALYZERS 300 MHz

Unangemessen

Laden...

Magazin per E-Mail verschicken

Laden...

Einbetten

Laden...

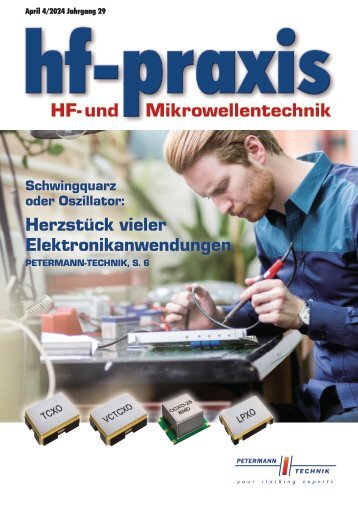

hf-praxis

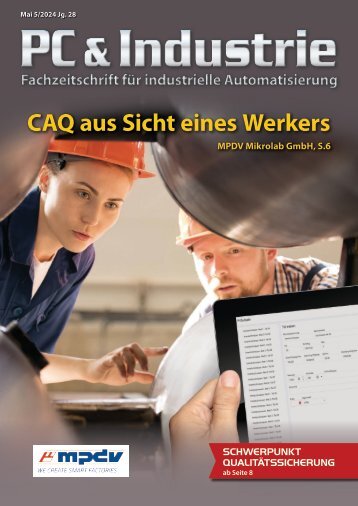

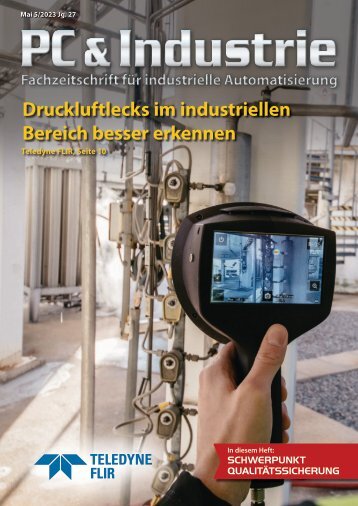

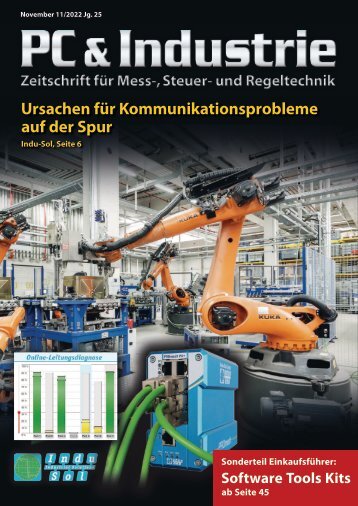

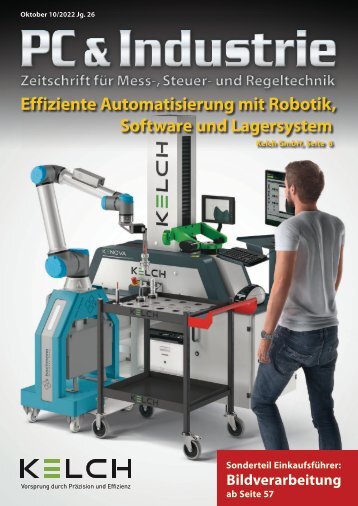

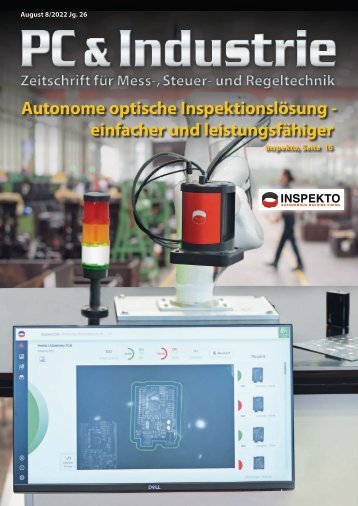

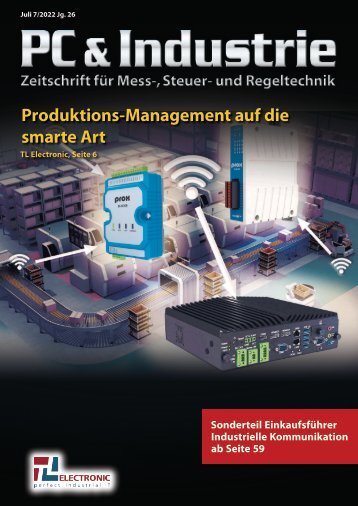

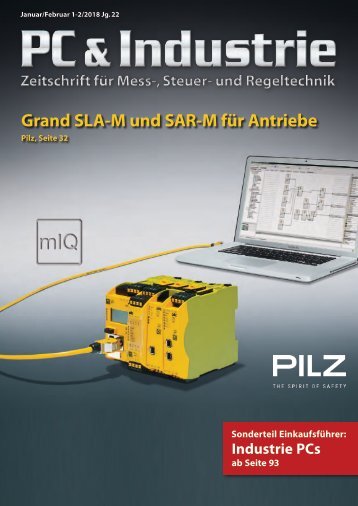

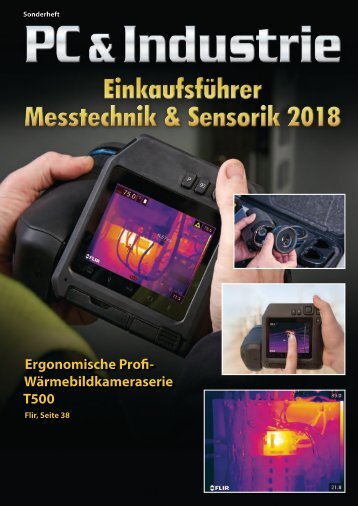

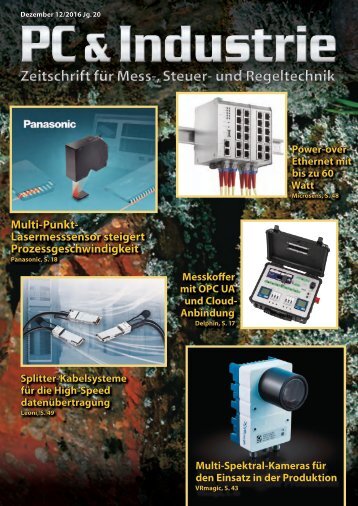

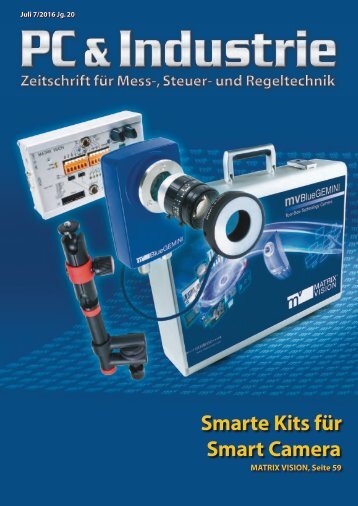

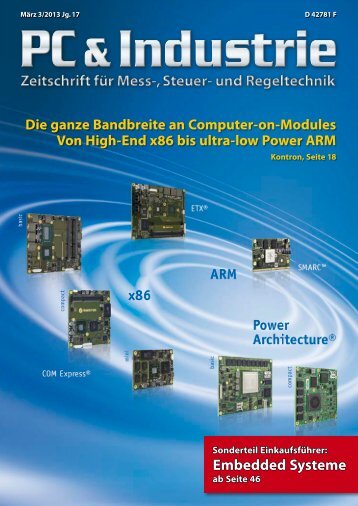

PC & Industrie

meditronic-journal

electronic fab

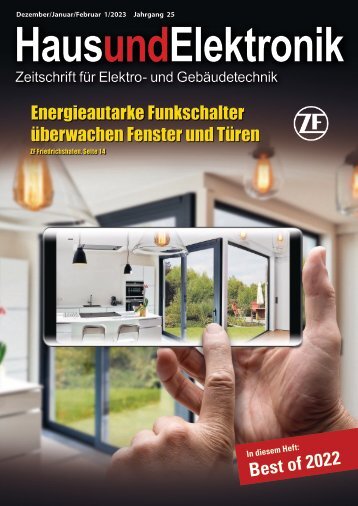

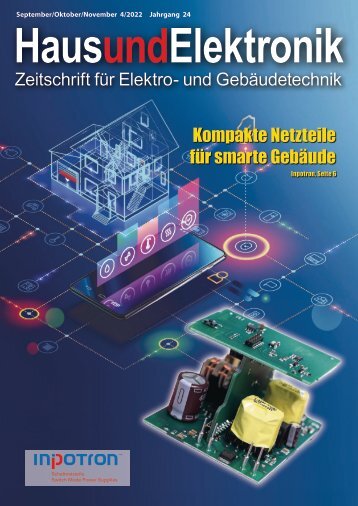

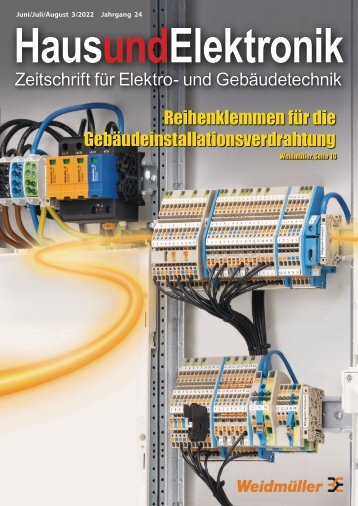

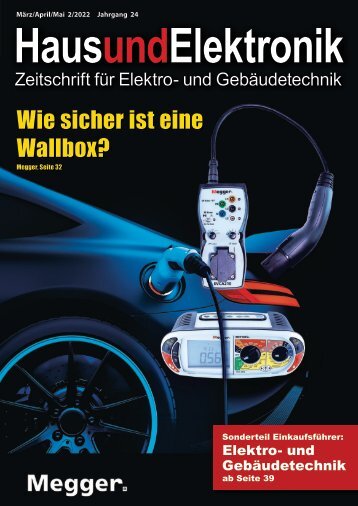

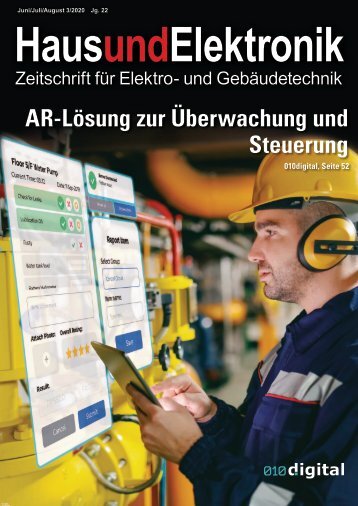

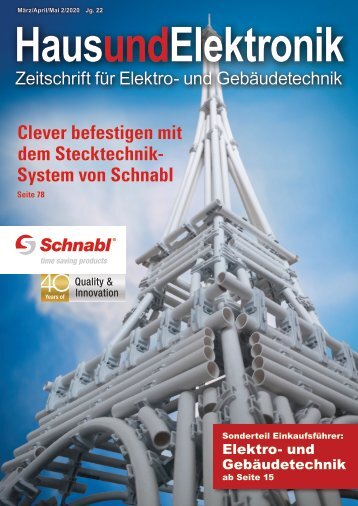

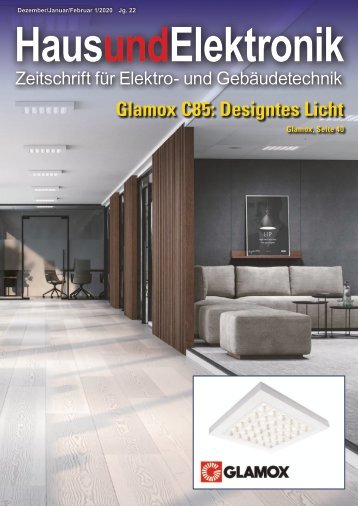

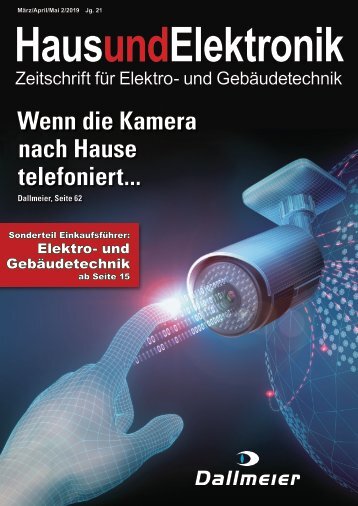

Haus und Elektronik

Mediadaten

© beam-Verlag Dipl.-Ing. Reinhard Birchel